L'IPC a publié de nouvelles exigences de placage pour permettre des largeurs de ligne plus fines.

Le tableau 3-10 ne nécessite désormais que 5 µm[197 µin] placage d'enveloppement minimum pour les vias enterrés> 2 couches, trous traversants et vias borgnes. Avant cette révision, l'épaisseur minimale de placage requise était de 12 µm.[472 µin] .

Cette nouvelle tolérance est utile aux fabricants de circuits imprimés, car elle leur permet de mieux répondre aux exigences de largeurs de lignes fines et d'espacement en constante évolution, propres à de nombreuses conceptions actuelles. En autorisant un placage minimum plus fin, les fabricants de circuits imprimés peuvent viser une couche de placage moins importante à la surface de la couche plaquée que la précédente révision. Cela permet de mieux contrôler les exigences d'espacement fin, car la quantité totale de cuivre à graver pour former les motifs et l'espacement du cuivre est réduite.

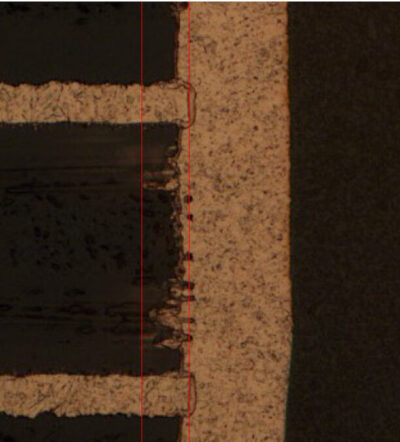

Tableau 3-10 Cuivre de surface et de trou minimum

Exigences relatives aux vias enterrés> Couches, trous traversants et vias borgnes

| Minimum absolu | 25 µm (984 µin) |

| Envelopper | 5 µm (197 µin) |

Remarque 1. Ne s'applique pas aux microvias (voir 1.4.4 de l'IPC-6012F)

Remarque 2. Le placage cuivre des PTH et des vias doit être conforme à la section 3.6.2.11.1 de l'IPC-6012F. L'AABUS est une alternative au placage cuivre.

Remarque 3. Voir 3.6.2.11 de l'IPC-6012F.