Protocoles de communication

Les **données série** circulent dans un circuit, de la **source à la destination**, sous forme de **tensions variables**.

L’émetteur **initie le changement** sur la ligne de signal, et le récepteur **détecte la modification du potentiel**.

Il existe **de nombreux protocoles** couramment utilisés dans l’industrie, notamment :

**ATA, SCSI, CAN, I²C, SPI, UART, RS232, RS485, USB, Ethernet, Microwire, 1-wire, etc.**

Cependant, les **capteurs commerciaux utilisent principalement I²C et SPI**.

Communication synchrone

La communication **synchrone** nécessite **au minimum deux lignes de signal** :

– Une ligne pour **les données**

– Une ligne pour **le signal d’horloge**

Communication asynchrone

La communication **asynchrone** nécessite **au moins une ligne de signal**.

Cependant, l’**émetteur et le récepteur doivent se mettre d’accord** sur la **fréquence d’horloge** avant d’établir la communication.

I²C

Le **RTC, le BNO055 et le BME280** communiquent avec **l’ATMega328 via I²C**.

Le protocole **Inter-Integrated Circuit (I²C)** utilise **deux lignes de données** :

– **SCL (Serial Clock Line)** : transmet l’information d’horloge

– **SDA (Serial Data Line)** : transmet les données

Le **maître** et l’**esclave** peuvent **déclencher la ligne de données**, mais **seul le maître contrôle l’horloge**.

Cela permet une communication **semi-duplex** entre le maître et l’esclave.

Avantages

L’un des **grands avantages** du protocole **I²C** est qu’il permet une communication **multi-maître, multi-esclave**.

Plusieurs **microcontrôleurs** peuvent être connectés au bus et lire les mêmes **données de capteurs**, tant qu’ils ne **contrôlent pas l’horloge simultanément**.

Cependant, **I²C est généralement utilisé** par un **seul microcontrôleur** pour communiquer avec plusieurs **périphériques esclaves** (EEPROM, capteurs, écrans, etc.).

Inconvénients

Conflits d’adresses

De nombreux **périphériques I²C** utilisent des **adresses sur 7 bits**.

Avec seulement **128 adresses possibles (2⁷ = 128, mais toutes ne sont pas utilisées)**, il est possible que **deux appareils aient la même adresse**.

Pour contourner ce problème, la plupart des fabricants ajoutent une **broche d’adresse (ADDR)** ou une **broche multifonction (MP)**, permettant de **modifier l’adresse** en changeant le **niveau logique** de la broche.

Capacitance

Un autre inconvénient du bus I²C est que **la haute capacité parasite** réduit la **vitesse de transmission**.

I²C est conçu pour une communication **relativement lente sur de courtes distances** (sur une même carte).

Bien qu’il puisse parfois être utilisé pour **relier deux cartes par fils**, il n’est **pas conçu pour cela**, surtout **à haute vitesse**.

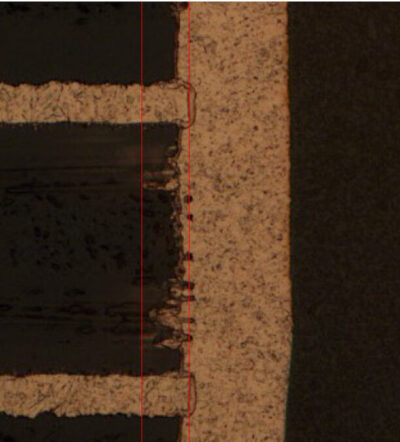

Considérations d’ingénierie pour I²C

Les **dispositifs maîtres I²C** **tirent directement** le signal logique à la **masse** et permettent aux **résistances de tirage** de ramener le signal au potentiel **Vcc**.

– La **transition de l’état haut à l’état bas** est **rapide** et ressemble à un **signal carré** sur un oscilloscope.

– La **transition de l’état bas à l’état haut** est influencée par **la capacité parasite du bus** et le choix des **résistances de tirage**.

Dans le bus **I²C**, la **constante de temps RC** de la **transition logique haute** **limite la vitesse du bus**.

– **La résistance** est fournie par les **résistances de tirage** et la **faible résistance des pistes**.

– **La capacité parasite** est **la somme** des **capacités des pistes**, des **broches des composants** et des **autres sources de capacitance**.

Selon la **spécification I²C**, la **capacitance maximale** autorisée est :

– **400 pF** en mode **Standard (100 kHz)** et **Fast (400 kHz)**

– **500 pF** en mode **Fast Plus (1 MHz)**

**400 pF est une valeur relativement faible**.

Par exemple :

– Une **broche d’entrée/sortie** a une capacitance d’environ **2-10 pF**.

– Une **piste de 6 mils sur un PCB FR-4** ajoute environ **2 pF par pouce** de longueur.

Logique binaire

La **logique binaire** a **deux états** : **haut** et **bas**.

– L’état **haut** correspond à une tension entre **70% et 100% de Vcc**.

– L’état **bas** correspond à une tension entre **0 et 30% de Vcc**.

– Entre **30% et 70% de Vcc**, l’état logique est **indéfini**.

(Ces seuils ne sont pas universels, mais constituent un bon point de départ.)

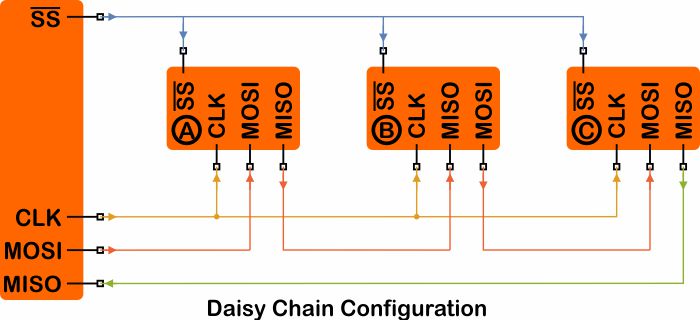

SPI

L’**ATMega328 communique avec l’écran via le bus SPI**.

Le **Serial Peripheral Interface (SPI)** est un protocole de **transfert de données synchrone bidirectionnel**.

Ce protocole nécessite **au moins trois lignes de données** :

– **MISO (Master In Slave Out)**

– **MOSI (Master Out Slave In)**

– **CLK (Clock)**

Une ligne supplémentaire appelée **Slave Select Not (SS̅)** est utilisée pour **activer/désactiver la transmission** sur un ou plusieurs circuits intégrés.

Le **trait supérieur (SS̅)** indique que **l’entrée numérique est inversée** :

– L’esclave est **activé** lorsque le **signal est bas**.

– Dans de nombreux cas, cette entrée peut être **connectée à la masse** pour **activer le bus en permanence**.

Les données stockées dans un registre à décalage linéaire sont déplacées bit par bit à chaque cycle d'horloge. SPI est un protocole full-duplex : l'émetteur et le récepteur peuvent transférer des données simultanément.

![]()

La spécification du bus série universel (USB) s'appuie sur la signalisation par paires différentielles pour transférer des données à haut débit. Une paire différentielle est constituée de deux lignes de signaux numériques de même amplitude mais de polarité opposée.

Règles de conception

Pour qu'une paire différentielle fonctionne comme prévu, les traces individuelles doivent avoir une largeur constante et un espacement constant par rapport aux autres conducteurs, et les deux traces doivent rester aussi identiques que possible, en suivant un chemin identique et en ayant la même longueur. L'idée générale est qu'une transition Low→Haut doit se propager le long du fil parallèlement et en même temps qu'une transition High→Low. Les champs électriques sont étroitement confinés entre les deux traces si les deux signaux parcourent la même distance sur le même diélectrique.

Si les pistes/fils ne sont pas de même longueur, ou si l'impédance du milieu environnant varie, la symétrie entre les deux fils est perdue, et une transition est en avance ou en retard sur l'autre. Lorsque les deux fils ont la même polarité, les champs électriques se repoussent et peuvent se propager plus loin.

Les interférences électromagnétiques sont le résultat de champs électromagnétiques à évolution rapide. Si les lignes de champ de la première animation changent pour ressembler à celles de la deuxième animation, ou inversement, la perturbation du champ électromagnétique se propagera de vos traces vers d'autres zones de votre circuit ou dans un environnement plus large. Le routage par paires différentielles a donc pour but de garantir que les deux fils restent aussi symétriques que possible sur une distance aussi égale et aussi courte que possible.

UART

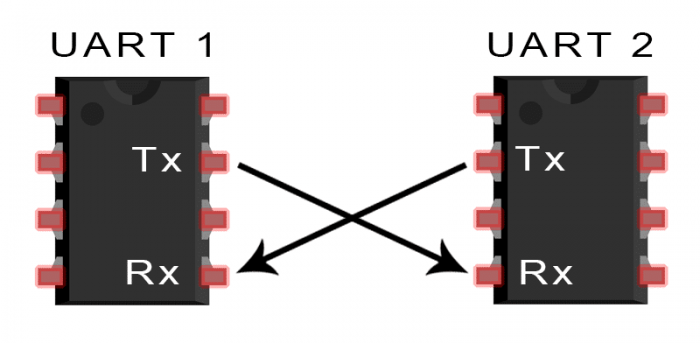

Le protocole de réception et de transmission asynchrones universels permet une communication en duplex intégral entre deux nœuds. La seule condition est que les deux nœuds conviennent d'un débit de transmission commun (débit en BAUDs).

Contrairement aux autres protocoles de communication utilisés dans notre conception, UART nécessite une connexion croisée. Transmettre→Recevoir et Recevoir→Transmettre.

Étant donné qu'il présente un taux de transmission relativement lent, les lignes de données UART peuvent parcourir toute la longueur d'un panneau PCB entier et hors carte via plusieurs mètres de câblage sans trop de problèmes.

Les nœuds de communication asynchrone tolèrent généralement une légère différence de synchronisation. Cependant, si les débits de transmission sont trop différents des débits de réception, les informations finissent par être brouillées. Si vous voyez des caractères aléatoires ou aucun caractère sur un écran de débogage série, le problème est généralement dû à une différence de synchronisation.