Et vous devriez vous défouler avec moi.

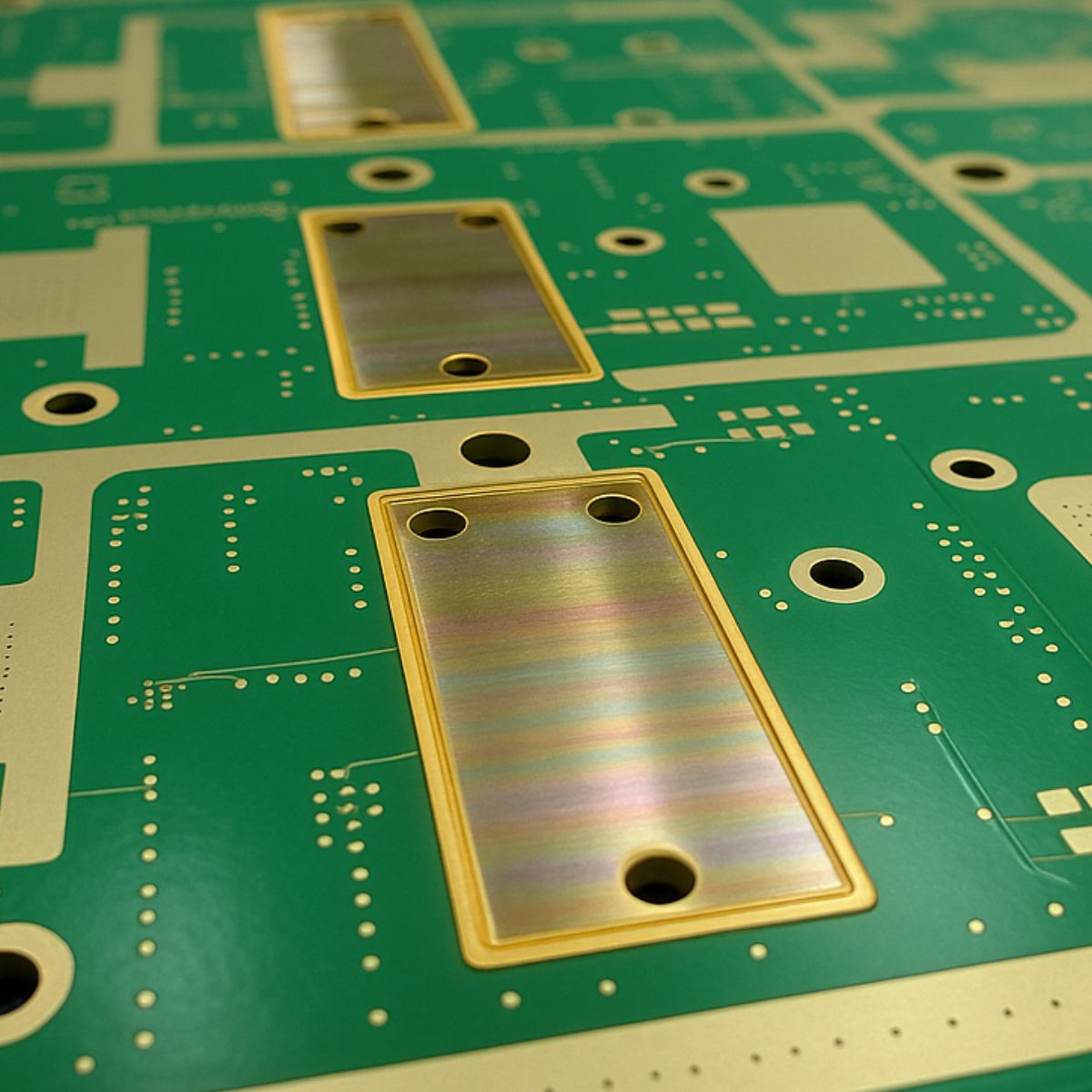

Conceptions HDI et plans de masse en cuivre solide ou presque solide, considérations de cuisson et de conception.

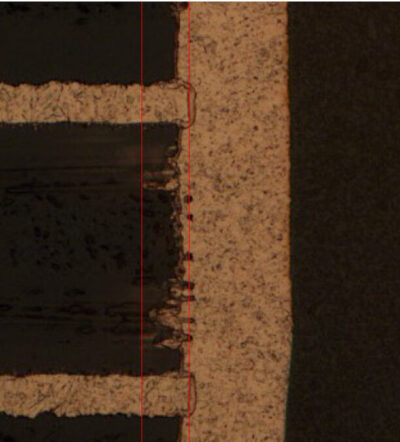

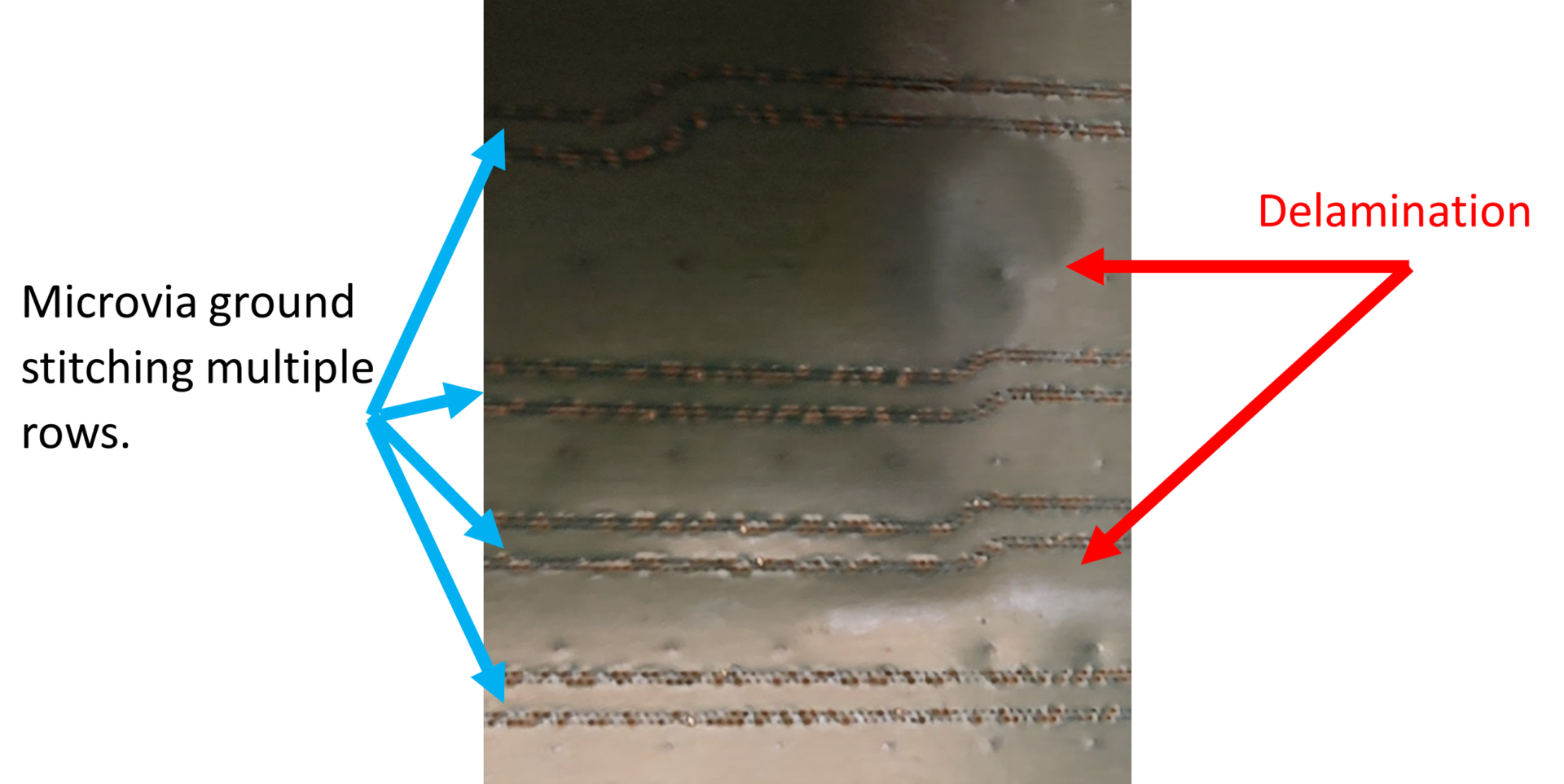

Au cours de l'année dernière, nous avons constaté des événements de délaminage inhabituels avec les conceptions HDI, en particulier avec les guides d'ondes coplanaires ou les conceptions numériques haute vitesse coplanaires. Les conceptions qui ont échoué contiennent de nombreux vias HDI avec de nombreuses combinaisons de portées de perçage, avec de larges zones sans relief de cuivre dans les couches planes ou très peu. La condition de conception comportera généralement de nombreuses rangées de points de mise à la terre qui sont des microvias fermés plaqués avec des structures de vias remplies d'époxy ou borgnes. Cette combinaison de pourcentage élevé de rétention de cuivre dans les couches et le traitement des microvias, des vias borgnes/enterrés ou remplis d'époxy créent une condition dans laquelle l'humidité de traitement est piégée dans le diélectrique entre les couches planes. S'il n'y a pas de relief de cuivre dans les couches verticales, alors la seule façon de faire sortir l'humidité est de cuire l'humidité par le côté du PCB. Cela peut inclure de très longues distances qui peuvent nécessiter plus de 24 à 72 heures de cuisson pour « déplacer » l'humidité hors du PCB.

La question est donc de savoir pourquoi cela ne s’est pas produit dans le passé ? En règle générale, une couche plane a 85 % ou moins de cuivre retenu sur toute la couche plane. Sans HDI ou vias aveugles, chaque trou plaqué qui s’étendait de la couche supérieure à la couche inférieure aurait des connexions sur certaines couches planes et un dégagement sur d’autres couches planes. Tous les trous plaqués de signal auraient un dégagement dans les deux couches planes. Les couches de signal auraient généralement 15 % de cuivre retenu, qui étaient toutes des connexions plaquées de signal. Compte tenu de ces attributs, il y avait toujours des voies verticales pour que l’humidité soit évacuée du diélectrique. Tout ce qui était nécessaire était de cuire au-dessus de l’ébullition pendant 6 heures et l’humidité a été éliminée ou réduite à un volume si faible qu’il n’y avait aucun risque de délamination pendant l’assemblage.

Découvrez pourquoi l’HDI et les couches de cuivre hautement retenues peuvent entraîner des résultats de délamination lors de la refusion.

Feuille de cuivre

Vous êtes-vous déjà demandé pourquoi nous utilisons l’épaisseur du cuivre en unités d’once ? L’histoire qu’on me raconte, c’est que le poids du cuivre en onces provient de l’industrie de la toiture. L’objectif principal de l’utilisation du cuivre comme matériau de toiture est d’empêcher la pluie (humidité) de pénétrer dans un bâtiment. La feuille de cuivre à 93 % ou plus agit comme une barrière contre l’humidité très efficace. Les conceptions HDI avec des microvias fermés plaqués ou avec ou sans vias aveugles/remplis d’époxy peuvent manquer de voies verticales.

Création de circuits coaxiaux

Dans le but de supprimer le bruit du signal et de concevoir des conceptions à plus hautes performances coplanaires, des couches planes solides sans relief en cuivre sont utilisées avec des vias assemblés au sol. Le défi se pose lorsque de nombreuses couches de coutures microvia et plusieurs rangées de microvia sont utilisées dans une conception.

Source de l’humidité

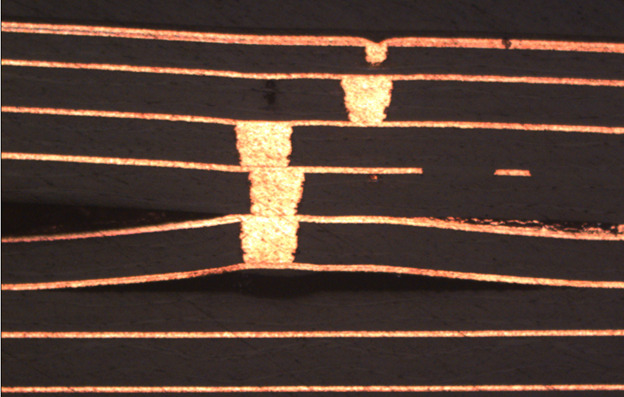

À partir du moment où une formation de perçage laser est terminée, le trou se lance dans environ 30 étapes de processus humide avant que la paroi du trou n’ait du cuivre galvanisé et scellé les parois latérales du via. À ce stade, l’humidité qui s’est infiltrée dans le stratifié a été stockée entre les couches planes (plus de 93 % de cuivre conservé) et plusieurs rangées de vias de couture au sol. Les multiples rangées de vias cousus au sol agissent comme un restricteur qui retarde et ralentit le mouvement de l’humidité. Pour éviter le délaminage, l’humidité doit être éliminée ou réduite à un niveau sûr. Il est devenu douloureusement évident que l’humidité est piégée entre les couches planes au-dessus et au-dessous du diélectrique et limitée dans son déplacement latéral à travers les multiples rangées de vias rectifiés plaqués.

Quelle quantité d’humidité peut pénétrer dans une microvia ?

Faisons le calcul. Si un microvia a un diamètre de 0,008 » et que l’épaisseur diélectrique est de 0,005 ». La quantité de surface exposée à absorber l’humidité est de 0,000125 carré / pouces. Dans le cas où la conception a des vias de couture au sol de 50k, la quantité de surface combinée est de 6,25 sq/pouces. À chaque processus humide entre le perçage au laser et le premier processus de galvanoplastie (30 étapes), le 6,25 pouces/carré absorbe de l’humidité. Une fois que le microvia a été galvanisé, l’humidité est piégée jusqu’à ce qu’un cycle de cuisson très long puisse être utilisé.

Si la conception comporte 200 000 microvias, la surface pouvant absorber de l’humidité est de 25 sq/pouces.

Comment atténuer le défi

Le cuivre se verse là où il est nécessaire, mais permet un relief de cuivre dans les couches planes à l’extérieur de votre guide d’ondes coplanaire. Le relief n’a pas besoin de traverser l’ensemble du PCB, mais un chemin vertical à proximité fera l’affaire.

Prévoyez plus de relief en cuivre dans les plans éloignés des sections de guide d’ondes coplanaires dans la conception.

Réduisez le nombre de rangées de points de sol ou le nombre de vias à la simple nécessité.

Prolongez la durée du cycle de cuisson à 24-72 heures au besoin. Ce n’est pas idéal pour l’état de surface et il y a une préoccupation accrue d’oxyder la finition de surface avant l’assemblage.

Si l’humidité n’est pas éliminée avant l’assemblage, le risque d’un délaminage existera. Autres exemples de délaminage dû à HDI : plusieurs rangées de coutures au sol et des couches planes avec plus de 93 % de surface de cuivre vendue au détail.