L'un des défis de la fabrication de circuits imprimés (PCB) réside dans l'apparition de vides de lamination, qui peuvent avoir un impact significatif sur les performances et la fiabilité du PCB final. Dans cet article de blog, nous explorerons les vides de lamination, leurs causes et les moyens d'en atténuer les effets.

Que sont les vides de stratification ?

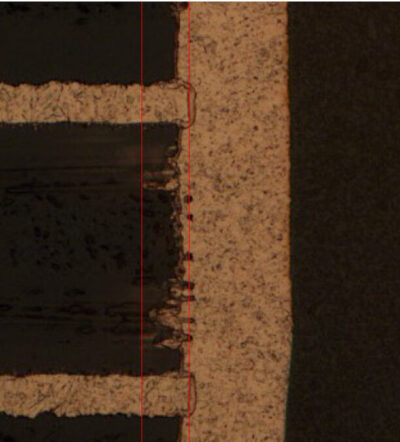

Les vides de lamination sont des zones de liaison incomplète entre les couches d'un circuit imprimé multicouche. Ces vides sont essentiellement des poches de gaz issues de la polymérisation thermique, causées par l'absence de résine époxy dans l'empilement du circuit imprimé. Leur taille et leur forme peuvent varier, et leur présence peut entraîner plusieurs problèmes, notamment une diminution de la conductivité thermique, une diminution de la résistance mécanique et une dégradation des performances électriques.

Causes des vides de stratification

Il est essentiel de comprendre les causes profondes de ces vides pour prévenir leur apparition. Les causes de délaminage sont les suivantes :

- Coefficient de dilatation thermique (CTE) inadapté : L'un des principaux facteurs responsables du délaminage est l'inadéquation entre les différents types de verre, dont les épaisseurs varient en fonction du CTE ppm/C, et l'absence d'encapsulation résine/verre utilisée dans le circuit imprimé. L'enthalpie du squelette de la résine et l'absorption d'humidité sont des facteurs qui provoquent une séparation cohésive après exposition thermique. Cela entraîne des contraintes sur les trous traversants métallisés.

- Variations environnementales et mécaniques : Le profil de laminage peut varier en fonction des conditions environnementales et des paramètres de la machine. Il est essentiel de définir correctement le profil avant de lancer le processus de laminage afin de minimiser la formation de vides.

- Valeurs de perçage inexactes : l'utilisation de valeurs de perçage incorrectes peut entraîner des vides car elles peuvent perturber la couverture du dépôt pendant les cycles de placage.

- Répartition inégale du cuivre : une répartition inégale du cuivre dans le circuit peut entraîner des cavités dans la résine. Pour atténuer ce problème, il est nécessaire d'ajouter suffisamment de cuivre (zones indésirables du circuit) pour équilibrer la répartition et ainsi réduire la formation de vides.

- Gaz piégés : Le contrôle de la température est essentiel lors du durcissement de la résine utilisée pour le laminage. Des profils de température incorrects peuvent entraîner une encapsulation incomplète et la formation de vides.

- Pression insuffisante : Une pression insuffisante pendant le processus de laminage empêche les couches de se lier correctement, ce qui entraîne des écarts qui conduisent à des vides.

- Contrôle de température inadéquat : Le contrôle de la température est essentiel lors du durcissement de la résine utilisée pour le laminage. Des profils de température incorrects peuvent entraîner un collage incomplet et la formation de vides.

- Contaminants : La présence de contaminants tels que les FOD, l'humidité ou les impuretés sur les surfaces de la résine ou des feuilles de cuivre peut interférer avec le processus de stratification et contribuer à la formation de vides.

- Mauvaise qualité des matériaux : L'utilisation de matériaux de mauvaise qualité, notamment les substrats et les préimprégnés, peut augmenter le risque de vides. Ces matériaux peuvent présenter une teneur en résine ou un renforcement irrégulier, ce qui les rend plus sensibles à la formation de vides.

Éviter les vides de plastification

Les vides de lamination peuvent nuire aux performances et à la fiabilité globales d'un circuit imprimé. Ils réduisent la conductivité thermique du circuit imprimé, ce qui entraîne une mauvaise dissipation thermique. Leur présence peut compromettre la résistance mécanique du circuit imprimé, provoquant des déformations, des fissures, voire une défaillance totale. Enfin, ils peuvent perturber l'intégrité du signal et l'adaptation d'impédance, entraînant des problèmes électriques. Cela peut entraîner une perte de signal, une augmentation des interférences électromagnétiques (EMI) et une diminution de la fonctionnalité globale. Une attention particulière portée aux empilements et à la répartition du cuivre sur la carte peut contribuer à minimiser l'apparition de vides de lamination.

Le rôle de la conception des empilements

Une conception d'empilement appropriée est essentielle pour éviter les vides de lamination des circuits imprimés. Une conception d'empilement bien pensée implique de sélectionner les bons matériaux et de les disposer de manière à minimiser les risques de formation de vides. Voici quelques points clés pour une conception d'empilement efficace :

- Sélection des matériaux : Le choix du matériau stratifié et du type de préimprégné adéquats est crucial. Privilégiez les matériaux à faible absorption d'humidité et à bonnes propriétés thermiques pour minimiser le risque de vides. De plus, l'utilisation de préimprégnés de haute qualité peut contribuer à prévenir les vides.

- Rapport cuivre/préimprégné : Le rapport cuivre/préimprégné est essentiel pour favoriser une bonne adhérence entre les couches. Le gaz est une masse qui doit être évacuée pour permettre à la résine/verre de se comprimer dessus, évitant ainsi les vides de stratification. Il est toutefois important de connaître la fenêtre d'écoulement de la résine avec une résistance minimale. Il s'agit par exemple de la vitesse d'élévation nécessaire pour atteindre ce seuil.< = 1 000 pascals. Plus la viscosité est faible, plus la résine est pure.

Le rôle de la distribution du cuivre

Outre la conception de l'empilement, la répartition du cuivre joue un rôle essentiel pour éviter les vides de lamination des circuits imprimés. Voici les points clés à prendre en compte pour une répartition efficace du cuivre :

- Répartition inégale de la pression : Une différence significative d'épaisseur de cuivre entre les différentes couches peut entraîner une répartition inégale de la pression lors du laminage. Un déséquilibre important peut entraîner la formation de vides dans les zones contenant moins de cuivre, car la pression peut ne pas être répartie uniformément.

- Utiliser des techniques de remplissage de cuivre : les techniques de remplissage de cuivre, telles que l'ajout de coulées de cuivre ou de plans de masse, peuvent aider à maintenir une distribution uniforme du cuivre tout en améliorant les performances thermiques.

En conclusion, les vides de lamination des circuits imprimés peuvent constituer un problème majeur, compromettant potentiellement la fonctionnalité et la fiabilité des appareils électroniques. Cependant, en se concentrant sur la conception de l'empilement et la répartition du cuivre, les concepteurs et les fabricants peuvent réduire considérablement le risque de formation de vides. La collaboration entre concepteurs et fabricants de circuits imprimés est essentielle pour garantir que les matériaux choisis, la configuration de l'empilement et la répartition du cuivre sont optimisés pour chaque projet spécifique, ce qui permet d'obtenir des circuits imprimés robustes et fiables pour un large éventail d'applications.